FPGA Based Design Lab

Task: Implement a 4X2 priority encoder using behavioral Modelling.

Module:

module priority (x,y,v,D);

output x,y,v;

reg x,y,v;

input [3:0] D;

always @(*)

begin

if(D==4'b0000)

begin v=0;

end

else if (D==4'b0001)

begin

x=0;y=0;v=1;

end

else if (D==4'b0010)

begin

x=0;y=1;v=1;

end

else if (D==4'b0100)

begin

x=1;y=0;v=1;

end

else if(D==4'b1000)

begin

x=1;y=1;v=1;

end

else $display ("syntax or logic error");

end

endmodule

Stimulus:

module stimulus;

wire x,y,v;

reg [3:0] D;

priority e1(x,y,v,D);

initial

begin

D=4'd0;

#10 D=4'b0001;

#10 D=4'b0010;

#10 D=4'b0100;

#10 D=4'b1000;

#10 $stop;

#10 $finish;

end

endmodule

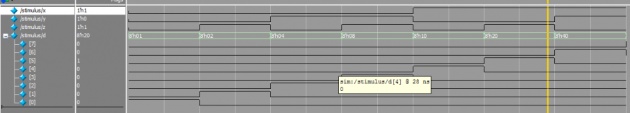

Obsrevation:

The Priority encoder converts the 4-bit input into a binary representation. If the input n is active, all lower inputs (n-1 ….. 0) are ignored (don’t care).

From above we observe that if we change the don’t care, outputs remains the same.

i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i ii i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i

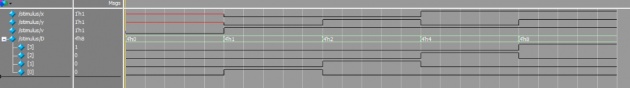

Task No.02: Implement the 8x3 encoder.

Module:

module encoder8 (d,x,y,z);

output x,y,z;

input [7:0] d;

reg x,y,z;

always @(*)

begin

if (d==8'd1)

begin x=0;y=0;z=0; end

else if (d==8'd2)

begin x=0;y=0;z=1; end

else if (d==8'd4)

begin x=0;y=1;z=0; end

else if (d==8'd8)

begin x=0;y=1;z=1; end

else if (d==8'd16)

begin x=1;y=0;z=0; end

else if (d==8'd32)

begin x=1;y=0;z=1; end

else if (d==8'd64)

begin x=1;y=1;z=0; end

else if (d==8'd128)

begin x=1;y=1;z=1; end

else $display ("don't care");

end

endmodule

Stimulus:

module stimulus;

wire x,y,z;

reg [7:0]d;

encoder8 encdr (d,x,y,z);

initial

begin

d=8'd1;

#10 d=8'd2;

#10 d=8'd4;

#10 d=8'd8;

#10 d=8'd16;

#10 d=8'd32;

#10 d=8'd64;

#10 d=8'd128;

$finish;

end

endmodule