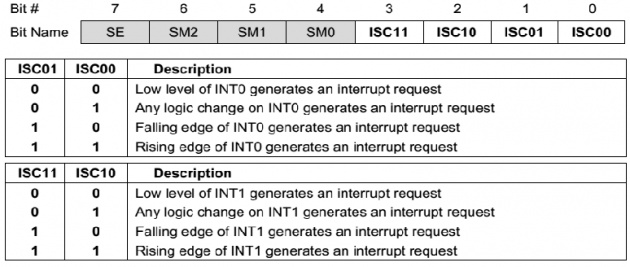

MCUCR(MCU Control Register)

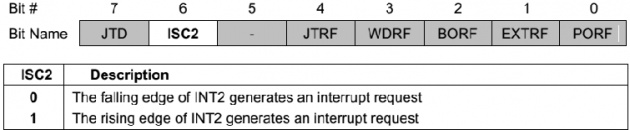

MCUCSR(MCU Control and Status Regiter)

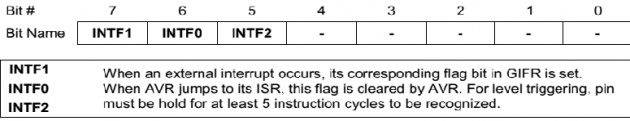

GIFR (General Interrupt Flag Register) has external interrupt flags. When an external interrupt is

occurs, corresponding flag of that external interrupt is raised. When microcontroller jumps of the

interrupt vector table, flag is automatically cleared or we can clear the flag by writing high on it.

GIFR(General Interrupt Flag Register)

Coding:

/*

This program generates a square wave of 5Hz (200ms) on PortA , Bit 0 using Timer0 CTC

interrupt. Moreover, at the same time, using External Hardware Interrupt INT2 is

configured on falling edge. Upon each INT2 falling edge interrupt, value of Port D is

incremented.

*/

#include<avr/io.h>

#include<avr/interrupt.h>

//Macros Definition

#define BitSet(p,m) ((p) |= (m))

#define BitClear(p, m) ((p) &= ~(m))

#define BitFlip(p,m) ((p) ^= (m))

#define Bit(x) (0x01 << (x))

int main(void)

{

DDRD = 0xFF; //Make PortD output

BitSet(DDRA, Bit(0)); //Make PA0 output

BitClear(DDRB, Bit(2)); //Make PB2 as input for INT2

BitSet(PORTB, Bit(2)); //Internally pull-up PB2

BitSet(TIMSK, Bit(1)); //Enable OC0IE bit to enable Timer0 Compare Mode interrupt

BitSet(GICR, Bit(5)); //Enable INT2 bit to enable External Interrupt 2

BitClear(MCUCSR, Bit(6));//Configure Falling edge triggered INT2 interrupt

sei(); //Enable Global Interrupt

OCR0 = 98; //98 calculated in the last lab for 0.1 seconds time

TCCR0 = 0x0D; //0000 1101, CTC Mode, Crystal Clock, 1024 prescaler

while(1); //Stay here forever

}

//Interrupt Service Routines (ISRs) of Timer0 CTC Mode & External Int errupt INT2

ISR (TIMER0_COMP_vect) //ISR for Timer0 CTC Output Compare

{

BitFlip(PORTA, Bit(0)); //Toggle PB0

}

ISR (INT2_vect) //ISR for External Interrupt INT2

{

PORTD++; //At every falling edge of INT2, increment Port D

}

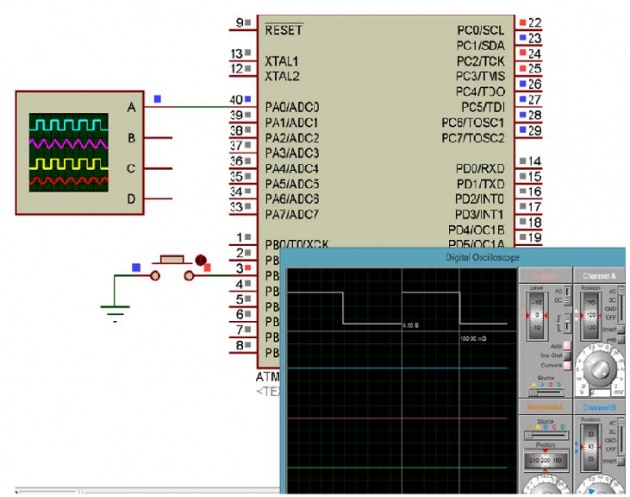

Simluation: