How to Make 4*8 Decoder in Verilog HDL in FPGA.

Data Flow Modeling module decoder_assign(a, y); input [3:0] a; output [7:0] y; assign y = ~a[0] & ~a[1] & ~a[2] & ~a[3];……

Data Flow Modeling module decoder_assign(a, y); input [3:0] a; output [7:0] y; assign y = ~a[0] & ~a[1] & ~a[2] & ~a[3];……

//This is the Main code. module decoder(d,x,y,z); output [7:0] d; input x,y,z; assign d[0] = ~x & ~y & ~z; assign d[1]……

//This is the Main code. module decoder(d,x,y,z); output [7:0] d; input x,y,z; assign d[0] = ~x & ~y & ~z; assign d[1]……

……

……

Main Module: module counter_16bit (q_out,co,count,clk,clr,value,load); output co; output [16:0] q_out; input clk,clr,count,load; input……

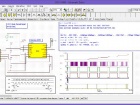

Task#01: Implement a 4X16 decoder using instantiation (use two 3X8 decoders).Simulate in either Xilinx ISE or Modelsim.Submit the……

Implement a 2X1 Mux using Gate-level Modeling. Simulate in either ModelSim or Xilinx ISE. Submit the code and wave files. Main Module……

Verilog is a Hardware discription language. A hardware description language is a computer language that is used to describe hardware.……